CS154 Computer Architecture Winter Term 2019

## Lab Assignment 04

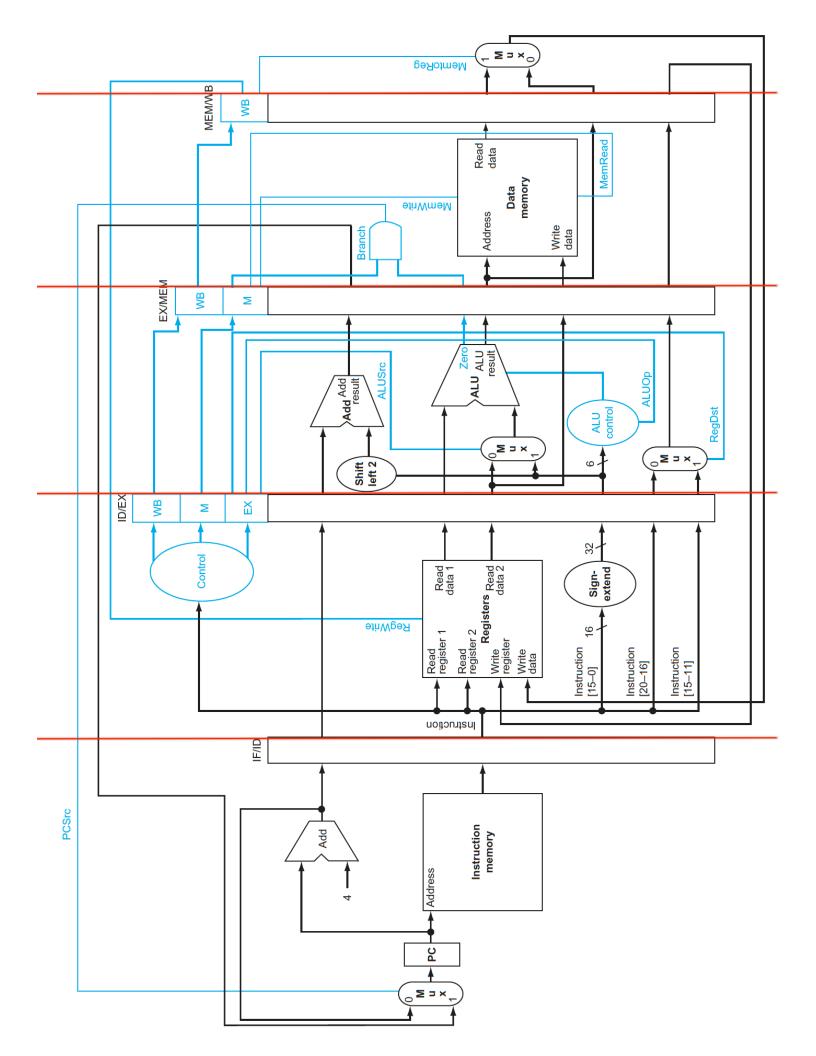

Consider the data path figure given below and in the next page:

Consider the following sequence of 7 instructions for the pipelined MIPS. Assume the pipeline is initially empty.

```

lw $t0, 0($s0)

lw $t1, 4($s0)

lw $t2, 8($s0)

addi $t0, $t0, 1

add $t1, $t1, $t2

sw $t0, 0($s0)

sw $t1, 4($s0)

```

Show the values of ALL data, address, and control line/bus values using this figure (you can make as many copies as needed), as the instructions follow through the stages of pipeline. Show the data and address lines more compactly using hexadecimal values. Draw a multiple-clock-cycle diagram (similar to Figure 4.52, in Page 305 on the book) to point out the cycles and units through which forwarding happens. Your grade depends on how complete the figures are in terms of the data, address, and control values, as these instructions move through the pipeline.